Bengaluru: Researchers at Indian Institute of Science (IISc), Bengaluru, have developed a compact hardware accelerator chip designed to support quantum-safe digital signatures, marking an important step toward securing future connected devices.

The chip is built to run SQIsign, a digital signature scheme that is being studied as a candidate for post-quantum cryptography standards. Current cryptographic systems rely on mathematical problems that are difficult for traditional computers to solve. However, experts warn that powerful quantum computers in the future could potentially break these protections.

To address this risk, researchers worldwide are working on post-quantum cryptography algorithms. While these methods are more resistant to quantum attacks, they often require greater computing power and communication resources.

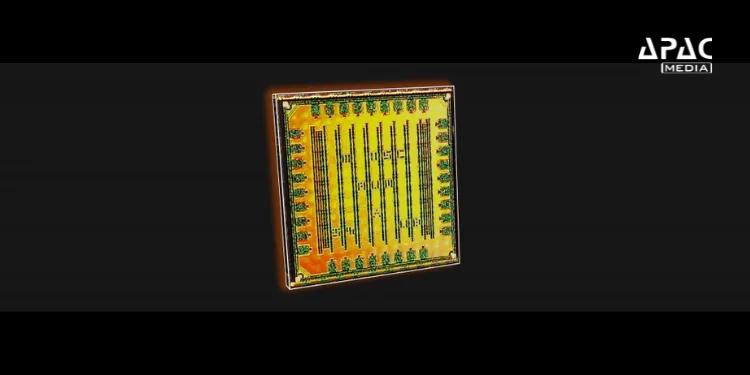

The IISc team designed a compact and energy-efficient chip that can handle these complex operations more effectively. The hardware accelerator was built using 28-nanometre CMOS technology and focuses on improving the verification of SQIsign signatures. According to the researchers, the chip delivers nearly ten times better performance and energy efficiency compared with advanced software-based implementations.

The technology could play an important role in securing Internet-connected devices. Applications include secure device boot processes, firmware updates, certificate validation and server authentication across IoT systems.

The research was presented at the IEEE International Solid-State Circuits Conference, a leading global forum for advanced semiconductor and system-on-chip technologies. Researchers say the work highlights the potential of hardware-accelerated quantum-safe cryptography and could guide future development of secure systems for connected devices.